I don't know adequate PAL simulator under Linux, at Windows only Proteus looks good, but i need it for testing ATF16V8B that i have. It looks like implement this with jed files as firmware will be easier than any MCU.

SPLD simulation

2 posters

2 Re: SPLD simulation Fri Jan 22, 2021 12:42 am

Re: SPLD simulation Fri Jan 22, 2021 12:42 am

arcachofo

I'm not familiar with JEDEC format, Not even with PLDs in general.

But jed files work for a concrete device.. isn't it?

If so then we need to implement JEDEC format and each one of these devices?

PLDs is not in the plans for now and this would require someone with deep knowledge of the topic, which is not me.

Anyway i'm open to collaborate.

But jed files work for a concrete device.. isn't it?

If so then we need to implement JEDEC format and each one of these devices?

PLDs is not in the plans for now and this would require someone with deep knowledge of the topic, which is not me.

Anyway i'm open to collaborate.

3 Re: SPLD simulation Fri Jan 22, 2021 8:53 am

Re: SPLD simulation Fri Jan 22, 2021 8:53 am

dvarkin

JEDEC File for SPLDs itself is described fairly simple, and this datasheet describes generated by fuses logical equations.

- JEDEC:

- II.3 JEDEC File

JEDEC means (J)oint (E)lectron (D)evice (E)nineering (C)ouncil.

This file is a ASCII file in which every bit which can be set in a

GAL is listed. The JEDEC file has the extension ".jed" and it's

generated by the GAL-Assembler.

The JEDEC file can start with any text until there is a asterisk (*).

The first '*' introduces the command field. The command field starts

with the first '*' and ends at the file end.

Within the command field are... (now be astonished) commands! A command

is introduced by one character and it ends with a '*' character.

All commands are optional. Not every command must be in a JEDEC file.

The GAL-Assembler normaly uses: L, F and G commands (see below)

Possible commands are:

N: This introduces a comment.

Example: N this is a comment *

^ ^ ^

| | |

command any text end of command

F: You don't have to list all states of the fuses in the GAL. If you don't

list all fuses GALer must know what the state of the missed fuses is.

F0 *: not listed fuses are set to 0

F1 *: not listed fuses are set to 1

G: Security Fuse

G0 *: don't set the security fuse after programming the GAL

G1 *: ask user (you) whether to set the security fuse after

programming the GAL or not

L: L defines the address of a fuse and what the state of the fuse

should be.

Example: L0000 10110111111111111111111111011111 *

this means: set fuse at address 0 to 1

set fuse at address 1 to 0

set fuse at address 2 to 1

.

.

.

possible addresses are:

GAL16V8, GA16V8A, GAL16V8B:

0000-2047: matrix of fuses (AND-array)

2048-2055: XOR bits

2056-2119: signature

2120-2127: AC1 bits

2128-2191: product term disable bits

2192 : SYN bit

2193 : AC0 bit

GAL20V8, GAL20V8A, GAL20V8B:

0000-2559: matrix of fuses (AND-array)

2560-2567: XOR bits

2568-2631: signature

2632-2639: AC1 bits

2640-2703: product term disable bits

2704 : SYN bit

2705 : AC0 bit

GAL22V10

0000-5807: matrix of fuses (AND-array)

5808-5827: S0/S1-bits of the OLMCs

5828-5891: signature

GAL20RA10

0000-3199: matrix of fuses (AND-array)

3200-3209: S0-bits of the OLMCs

3210-3273: signature

QF: Defines how many fuses in the JEDEC file are. A GAL16V8 has

2194 fuses and a GAL20V8 has 2706 fuses. Now GALer can

identify for which type of GAL this JEDEC file is.

Example: QF2194 *

C: C is followed by a 16 bit hex number which is the fuse checksum of

the JEDEC file (see description of menu 'JEDEC file parameter').

Example: C6402 *

, : These are control characters.

: 0x02 = CTRL-B

: 0x03 = CTRL-C

Your text editor displays this characters in this way:

defines the start of the JEDEC file and the end of the

JEDEC file. is followed by the file checksum (see description

of menu 'JEDEC file-parameter'). The file checksum is a 16 bit hex

number.

V: V introduces a test vector. GALer 1.4 does not support this. GALer

interprets this command as a N command (comment).

4 Re: SPLD simulation Fri Jan 22, 2021 11:19 am

Re: SPLD simulation Fri Jan 22, 2021 11:19 am

arcachofo

Right now I have 0 time to get into this, but this probably could be solved with the "Function" component or a derivative of it.

So.. from the jed file you can get a combinational function for each output?

Like:

Out1 = (In1 & !In2 & In3 ...) | (!In1 & In2 & In3 ...) ...

Out2 = (!In1 & In2 & !In3 ...) | (!In1 & !In2 & In3 ...) ...

...

So.. from the jed file you can get a combinational function for each output?

Like:

Out1 = (In1 & !In2 & In3 ...) | (!In1 & In2 & In3 ...) ...

Out2 = (!In1 & In2 & !In3 ...) | (!In1 & !In2 & In3 ...) ...

...

5 Re: SPLD simulation Fri Jan 22, 2021 11:36 am

Re: SPLD simulation Fri Jan 22, 2021 11:36 am

dvarkin

Yes, also ATF16V8B in the registred mode has registred outputs, tri-stated by the /OE pin and clocked by the Clock pin, in the combinational configuration of output and in the complex mode tri-stating of each output is function too, and almost always outputs have feedback to the AND-array.

6 Re: SPLD simulation Fri Jan 22, 2021 12:44 pm

Re: SPLD simulation Fri Jan 22, 2021 12:44 pm

arcachofo

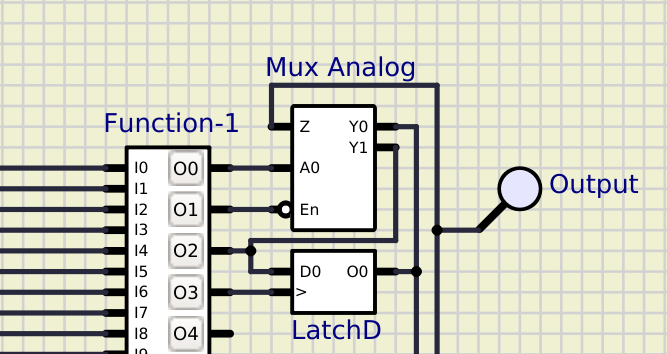

This could be implemented in a subcircuit containing:

- One Input Latch to implement the Clock.

- One Function Component to implement the combinational stuff, with:

One output dedicated to control OE.

- One Output Latch to implement the OE for each output.

Have a look to the Function component: https://www.simulide.com/p/function-component.html

What is needed is a program that can convert jed files to functions readable by the function component.

Then experimentig a bit with it.

- One Input Latch to implement the Clock.

- One Function Component to implement the combinational stuff, with:

One output dedicated to control OE.

- One Output Latch to implement the OE for each output.

Have a look to the Function component: https://www.simulide.com/p/function-component.html

What is needed is a program that can convert jed files to functions readable by the function component.

Then experimentig a bit with it.

7 Re: SPLD simulation Fri Jan 22, 2021 2:30 pm

Re: SPLD simulation Fri Jan 22, 2021 2:30 pm

arcachofo

Here is a very rought idea without the clocked outputs.

Now you need the functions that determine output values, which outputs have feedback, which input controls OE and so on.

Then get it into a subcircuit.

O0 controls channel 0 OE

O1 controls channel 0 Output value

O2 controls channel 1 OE

O3 controls channel 1 Output value

...

I10 is channel 0 feedback

I11 is channel 0 as input

I12 is channel 1 feedback

I13 is channel 1 as input

...

Now you need the functions that determine output values, which outputs have feedback, which input controls OE and so on.

Then get it into a subcircuit.

O0 controls channel 0 OE

O1 controls channel 0 Output value

O2 controls channel 1 OE

O3 controls channel 1 Output value

...

I10 is channel 0 feedback

I11 is channel 0 as input

I12 is channel 1 feedback

I13 is channel 1 as input

...

8 Re: SPLD simulation Sun Jan 24, 2021 7:30 am

Re: SPLD simulation Sun Jan 24, 2021 7:30 am

dvarkin

Interesting...

Feedback from function is not needed, feedback from buffers does all the things.

And I need to testing mostly SPLD in registered mode, where each output may be registered or not dependent on fuses. It can be made with function component too...

And on power up registers are set high...

PS: And place ATmega instead of function component, registers and buffers may be easier way

Feedback from function is not needed, feedback from buffers does all the things.

And I need to testing mostly SPLD in registered mode, where each output may be registered or not dependent on fuses. It can be made with function component too...

And on power up registers are set high...

PS: And place ATmega instead of function component, registers and buffers may be easier way

9 Re: SPLD simulation Sun Jan 24, 2021 9:33 am

Re: SPLD simulation Sun Jan 24, 2021 9:33 am

arcachofo

Yes, that was a rought idea without the clocked registers.Feedback from function is not needed, feedback from buffers does all the things.

And I need to testing mostly SPLD in registered mode, where each output may be registered or not dependent on fuses.

With registers could be something like this (for each channel):

Would be simpler circuit, but you need to write a program for that ATmega...PS: And place ATmega instead of function component, registers and buffers may be easier way

10 Re: SPLD simulation Sun Jan 24, 2021 9:37 am

Re: SPLD simulation Sun Jan 24, 2021 9:37 am

dvarkin

And I can send jedec directly to that ATmega over UART...

11 Re: SPLD simulation Sun Jan 24, 2021 10:43 am

Re: SPLD simulation Sun Jan 24, 2021 10:43 am

arcachofo

To use an Atmega you should write a program that:

And place ATmega instead of function component, registers and buffers may be easier way

And I can send jedec directly to that ATmega over UART...

- Receive data over uart.

- Convert that data to something usable (likely functions).

- And emulates your device: read inputs, apply funtions, set outputs.

In my opinion, it is the same effort writting a program for a dedicated component in simulide, which is far better.

The subcircuit aproach is easier because you don't need to write a program that emulates the device.

You only need to convert jed files to functions.

But is much slower than a dedicated component.

So each aproach has it's pros and cons...

12 Re: SPLD simulation Sun Jan 24, 2021 11:42 am

Re: SPLD simulation Sun Jan 24, 2021 11:42 am

dvarkin

I can use recieved fuse map only instead converting jedec to functions, see PAL architecture.

Each 8 rows of fuses described in jedec file define Disjunctive normal form (sum-of-products) function of each output (flip flop input). Bitwise operations might to do all the things.

Each 8 rows of fuses described in jedec file define Disjunctive normal form (sum-of-products) function of each output (flip flop input). Bitwise operations might to do all the things.

13 Re: SPLD simulation Sun Jan 24, 2021 12:26 pm

Re: SPLD simulation Sun Jan 24, 2021 12:26 pm

arcachofo

What about the .sim file?

Do you have some example of a file like this but with registered outputs?

- Code:

%SIGNAL

PIN 16 = A

PIN 15 = B

PIN 14 = C

PIN 13 = D

PIN 12 = E

PIN 18 = F

PIN 17 = G

PIN 8 = I0

PIN 2 = I1

PIN 3 = I2

PIN 7 = I3

%END

%FIELD

FIELD INPUT = I3,I2,I1,I0

FIELD OUTPUT = A,B,C,D,E,F,G

%END

%EQUATION

A =>

I0 & !I1 & I2 & I3

# I0 & !I1 & !I2 & !I3

# !I0 & !I1 & I2 & !I3

# I0 & I1 & !I2 & I3

B =>

!I0 & !I1 & I2 & I3

# I0 & !I1 & I2 & !I3

# !I0 & I1 & I2

# I0 & I1 & I3

C =>

I0 & I1 & I2 & I3

# !I0 & I1 & !I2 & !I3

# !I0 & I2 & I3

D =>

!I0 & I1 & !I2 & I3

# I0 & !I1 & !I2

# !I0 & !I1 & I2 & !I3

# I0 & I1 & I2

E =>

I0 & !I1 & !I2 & I3

# I0 & !I2 & !I3

# !I1 & I2 & !I3

# I0 & I1 & I2 & !I3

F =>

I0 & !I1 & I2 & I3

# I0 & !I2 & !I3

# !I0 & I1 & !I2 & !I3

# I0 & I1 & I2 & !I3

G =>

!I1 & !I2 & !I3

# !I0 & !I1 & I2 & I3

# I0 & I1 & I2 & !I3

%END

Do you have some example of a file like this but with registered outputs?

14 Re: SPLD simulation Sun Jan 24, 2021 1:56 pm

Re: SPLD simulation Sun Jan 24, 2021 1:56 pm

dvarkin

I don't use assemblers with simulator, I am use GALasm, in it registered outputs have «.R» suffix, that's all.

In your .sim file it will be so.

In your .sim file it will be so.

15 Re: SPLD simulation Sun Jan 24, 2021 2:14 pm

Re: SPLD simulation Sun Jan 24, 2021 2:14 pm

dvarkin

Also I have project with 16V8 in registered mode: GAL14500, but it hasn't something like sim files.

Also see GALasm examples in galer directory of it's git repo - galasm hasn't complicated language constructions.

Also see GALasm examples in galer directory of it's git repo - galasm hasn't complicated language constructions.

16 Re: SPLD simulation Sun Jan 24, 2021 7:07 pm

Re: SPLD simulation Sun Jan 24, 2021 7:07 pm

arcachofo

Can you write a javascript program that does that?I can use recieved fuse map only instead converting jedec to functions,

...

Bitwise operations might to do all the things.

17 Re: SPLD simulation Sun Jan 24, 2021 8:34 pm

Re: SPLD simulation Sun Jan 24, 2021 8:34 pm

arcachofo

I just had a look at some examples, and i see you already have the functions in the .pld file:

It is simpler than i expected.

- Code:

B C D E F G H I J GND

K NC NC NC Z Y X W A VCC

W = A * B * C

/X = D * E

Y = F + G

Z = H * I + J * K

It is simpler than i expected.

18 Re: SPLD simulation Mon Jan 25, 2021 3:13 am

Re: SPLD simulation Mon Jan 25, 2021 3:13 am

dvarkin

I am not sure about JavaScript, but see galemu - CLI (not useful in registered mode) and qt4 (I can't install it with qt5) 22v10 (more complicated than 16v8) emulator written in Python.

I like assembler and uC more than JavaScript, I prefer made simple program for ATmega. Jedec files contain almost same information as galasm files.

Book with funny pictures.

I like assembler and uC more than JavaScript, I prefer made simple program for ATmega. Jedec files contain almost same information as galasm files.

Book with funny pictures.

19 Re: SPLD simulation Mon Jan 25, 2021 10:14 am

Re: SPLD simulation Mon Jan 25, 2021 10:14 am

arcachofo

Nice.

I like assembler and uC more than JavaScript, I prefer made simple program for ATmega. Jedec files contain almost same information as galasm files.

And you send the data with an existing programer or something like that?

20 Re: SPLD simulation Wed Feb 03, 2021 10:26 am

Re: SPLD simulation Wed Feb 03, 2021 10:26 am

dvarkin

I think I can use something like Arduino bootloader for receive jedec data over UART to large Flash memory - jedec already has checksums.

Similar topics

Permissions in this forum:

You cannot reply to topics in this forum

Latest images

Latest images