Thread to discuss and report about PIC enhanced MId-Range core and 16F1826.

These will be be steps: (*) = Done:

(*)1- "Dummy" enhanced core and 16F1826:

This will be the base to start adding things.

The "Dummy" enhanced core will be a subclass of the old midrange core, so an exact copy.

From here I will add new instructions and other features.

(*)2- Implement new instructions and make the cpu functional.

- Rough implementation of new instructions is done ( not tested ).

3- Test the cpu and solve issues:

Looks to be working, but need more testing.

4- Start to add perifericals...

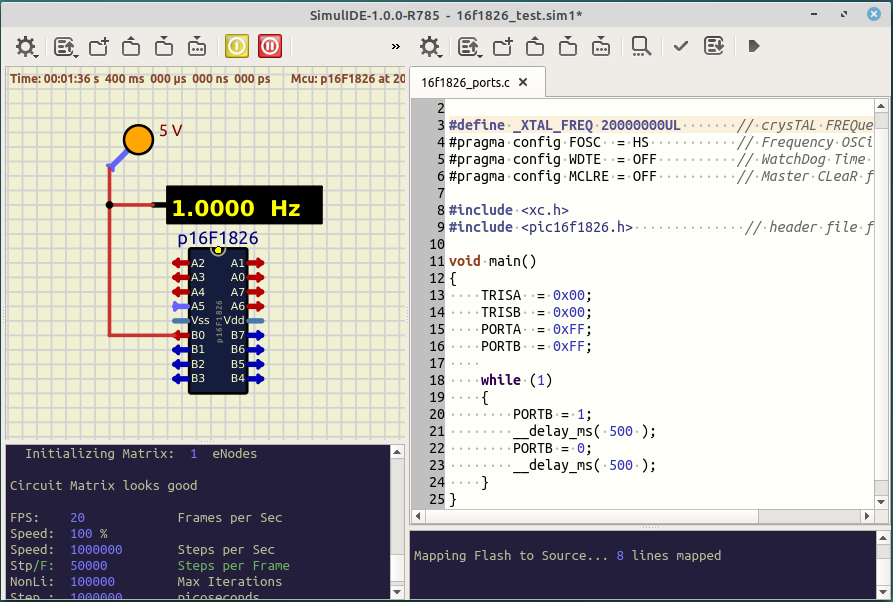

(*)- Ports: done.

(*)- ADC: New variant..

(*)- Eusart: basic implementation done.

(*)- Timer0: Using existing variant.

(*)- Timer1: New variant.

(*)- Timer2: Using existing variant.

- Comparators: Need new variants.

5- Testing Perifericals:

Ports:

(*)- Basic Read/Write OK.

- PORTA5 only input.

(*)- Pullups.

- Analog Pins.

(*)- INT interrupt.

- IOC interrupt.

(*)- Clock Pins.

- Reset Pin.

Eusart:

(*)- Basic: Serial Monitor shows send & received data.

(*)- Communication betwen 2 16f1826.

- Baudrate.

- Interrupt.

- Change Pins.

ADC:

(*)- Basic reading OK

(*)- Interrupt OK

(*)- Left/Right justified OK.

(*)- Prescaler: implementation not finished.

(*)- Vref.

DAC:

(*)- Basic operation.

(*)- Voltage Output.

(*)- Vref.

TIMER0:

(*)- Basic timer operation (internal clock).

(*)- Prescaler.

(*)- Interrupt.

(*)- External clock.

- External clock edge selection.

TIMER1:

(*)- Basic timer operation (internal clock).

(*)- Prescaler.

(*)- Interrupt.

(*)- External clock.

- External clock edge selection.

TIMER2:

(*)- Basic timer operation.

(*)- Prescaler.

(*)- Interrupt.

Note: With XC8 compiler it breaks __delay_ms()

____________________________________________

Perifericals:

To find if a periferiacl is already implemented you need to use this file:

SimulIDE_1.0.0-Rxx/data/PIC/pic/types

It is still very incomplete, but I will update it soon.

In that file you can see the existing variants for each periferical.

For example ADC:

- Type 00: p16F87x.

- Type 10: p16F88x.

- Type 11: p12F675.

You can see that there are 3 variant implemented and which models use it.

So in 16F1826 datasheet go to ADC section and compare it with the datasheet of those in the list.

- You can have a look at the block diagram to have a general idea.

- Then you need to compare the registers used: register names, bit names and their functionality.

In some cases you will find one that is exactly the same (very unlikely in this case).

In most cases there is one that is similar but with some diffrences.

For exaple in this case you will find that the most similar ADC is p16F88x.

But there are some differences in ADCON0 and ADCON1.

For example:

- ADCON bits moved from ADCON0 to ADCON1 and there are 3 bits instead of 2.

- Vref selection is done with ADPREF bits instead of VCFG, and there are 5 options instead of 4.

With this information I will create a new ADC variant that will also be used in future models.

These will be be steps: (*) = Done:

(*)1- "Dummy" enhanced core and 16F1826:

This will be the base to start adding things.

The "Dummy" enhanced core will be a subclass of the old midrange core, so an exact copy.

From here I will add new instructions and other features.

(*)2- Implement new instructions and make the cpu functional.

- Rough implementation of new instructions is done ( not tested ).

3- Test the cpu and solve issues:

Looks to be working, but need more testing.

4- Start to add perifericals...

(*)- Ports: done.

(*)- ADC: New variant..

(*)- Eusart: basic implementation done.

(*)- Timer0: Using existing variant.

(*)- Timer1: New variant.

(*)- Timer2: Using existing variant.

- Comparators: Need new variants.

5- Testing Perifericals:

Ports:

(*)- Basic Read/Write OK.

- PORTA5 only input.

(*)- Pullups.

- Analog Pins.

(*)- INT interrupt.

- IOC interrupt.

(*)- Clock Pins.

- Reset Pin.

Eusart:

(*)- Basic: Serial Monitor shows send & received data.

(*)- Communication betwen 2 16f1826.

- Baudrate.

- Interrupt.

- Change Pins.

ADC:

(*)- Basic reading OK

(*)- Interrupt OK

(*)- Left/Right justified OK.

(*)- Prescaler: implementation not finished.

(*)- Vref.

DAC:

(*)- Basic operation.

(*)- Voltage Output.

(*)- Vref.

TIMER0:

(*)- Basic timer operation (internal clock).

(*)- Prescaler.

(*)- Interrupt.

(*)- External clock.

- External clock edge selection.

TIMER1:

(*)- Basic timer operation (internal clock).

(*)- Prescaler.

(*)- Interrupt.

(*)- External clock.

- External clock edge selection.

TIMER2:

(*)- Basic timer operation.

(*)- Prescaler.

(*)- Interrupt.

Note: With XC8 compiler it breaks __delay_ms()

____________________________________________

Perifericals:

To find if a periferiacl is already implemented you need to use this file:

SimulIDE_1.0.0-Rxx/data/PIC/pic/types

It is still very incomplete, but I will update it soon.

In that file you can see the existing variants for each periferical.

For example ADC:

- Type 00: p16F87x.

- Type 10: p16F88x.

- Type 11: p12F675.

You can see that there are 3 variant implemented and which models use it.

So in 16F1826 datasheet go to ADC section and compare it with the datasheet of those in the list.

- You can have a look at the block diagram to have a general idea.

- Then you need to compare the registers used: register names, bit names and their functionality.

In some cases you will find one that is exactly the same (very unlikely in this case).

In most cases there is one that is similar but with some diffrences.

For exaple in this case you will find that the most similar ADC is p16F88x.

But there are some differences in ADCON0 and ADCON1.

For example:

- ADCON bits moved from ADCON0 to ADCON1 and there are 3 bits instead of 2.

- Vref selection is done with ADPREF bits instead of VCFG, and there are 5 options instead of 4.

With this information I will create a new ADC variant that will also be used in future models.

Last edited by arcachofo on Sun Dec 17, 2023 1:05 pm; edited 22 times in total (Reason for editing : Added information.)

Latest images

Latest images