When TWI and Timer0 are used from AVR core, it seems that the core "resets" continuously, once a signal gets received.

I have two outputs included: ok signal in main-loop (PORTB0) and (re)start signal ahead of the main loop (PORTB1).

The (re)start signal should there be only once, but appears continuously after receiving a signal

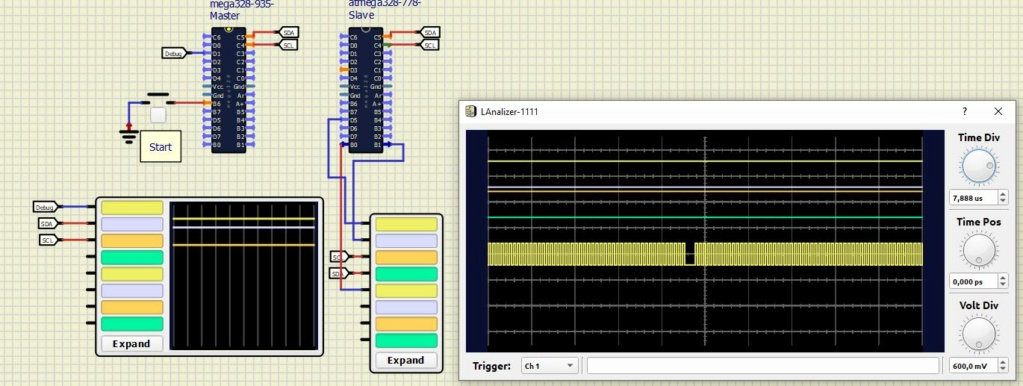

OK Situation

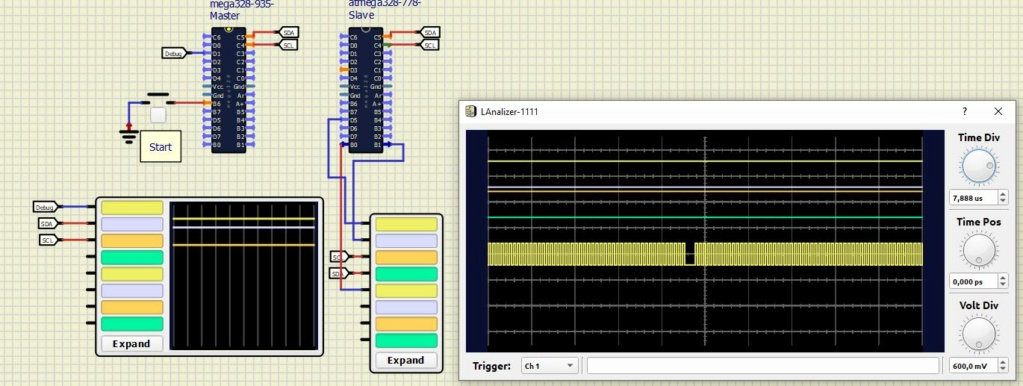

Resetting Situation after pushing start button

The problem appears in R927 and younger until the R977.

The version R872 and older don't show the problem.

There is also another minor bug: When triggering the righthand logic analyzer on Ch4 (SDA), once triggered (=pushing start) the ok-signal (yellow one) disappears.

I have two outputs included: ok signal in main-loop (PORTB0) and (re)start signal ahead of the main loop (PORTB1).

The (re)start signal should there be only once, but appears continuously after receiving a signal

OK Situation

Resetting Situation after pushing start button

The problem appears in R927 and younger until the R977.

The version R872 and older don't show the problem.

There is also another minor bug: When triggering the righthand logic analyzer on Ch4 (SDA), once triggered (=pushing start) the ok-signal (yellow one) disappears.

- Attachments

I2C_timer.zip

I2C_timer.zip - You don't have permission to download attachments.

- (4 Kb) Downloaded 2 times

Latest images

Latest images

...

...